Как тестировать сложную цифровую технику? Возможности стандарта JTAG IEEE 1149.1

С развитием электронной промышленности и объемов производства все более неизбежной становится задача тестирования электронных изделий. Старые подходы к проверке качества и работоспособности становятся все менее актуальными. До сих пор производители и заказчики электроники привыкли производить функциональное тестирование продукции и, при наличии отказавших изделий, проводить диагностику неисправностей с привлечением высококвалифицированного персонала, в том числе разработчиков.

С развитием электронной промышленности и объемов производства все более неизбежной становится задача тестирования электронных изделий. Старые подходы к проверке качества и работоспособности становятся все менее актуальными. До сих пор производители и заказчики электроники привыкли производить функциональное тестирование продукции и, при наличии отказавших изделий, проводить диагностику неисправностей с привлечением высококвалифицированного персонала, в том числе разработчиков.

Порой отказы могут проявляться на самых финальных стадиях производства. Возрастающая сложность печатных узлов делает функциональный тест все менее информативным и более длительным. К тому же процесс его создания ложится на плечи разработчиков – людей, имеющих ограниченный ресурс времени. Поэтому зачастую при проверке новых типов изделий используются устаревшие тесты. В результате страдает качество продукции, возникают непредвиденные отказы оборудования у потребителя, на разработчиков ложится груда работы по выявлению причин отказов (или, как вариант, предприятие содержит большой штат специалистов по ремонту, а также немалое количество специализированного оборудования).

Структурное тестирование

Для того чтобы избежать всех этих проблем, мировые производители электроники уже много лет используют стратегию структурного тестирования, которая подразумевает не проверку функционирования изделия, а, скорее, тестирование качества его сборки и соответствия конструкторской документации. Сами тесты и их разработка чаще всего производятся в автоматическом режиме. Данная стратегия избавляет разработчика от рутины создания тестов, позволяет на ранних стадиях определять дефекты и ошибки монтажа с точностью до компонента или вывода микросхемы, делает процессы производства и разработки изделий более гибкими и простыми. Совсем не обязательно при этом отказываться от функционального тестирования, оно может использоваться, например, при окончательной проверке изделий и предъявлении их ОТК.

ICT

Один из видов структурного тестирования – внутрисхемное тестирование – производится при помощи автоматического тестера и поля контактов игольчатого типа. Если тестируемая плата имеет достаточное количество контактных площадок, то можно добиться практически стопроцентного тестового покрытия – локализации непропаев, коротких замыканий, проверки наличия или отсутствия компонентов, а также измерить номиналы. Неудивительно, что данный метод достаточно долго занимал ведущие позиции в области тестирования во всем мире.

Но прогресс не стоит на месте, изделия электроники становятся все более миниатюрными, и, порой, на плате с высокой плотностью монтажа нет возможности разместить и пары десятков контактных площадок. К тому же появились новые типы корпусов, такие как QFP, BGA, CSP и т.д., тестовый доступ к выводам которых вообще не возможен при помощи поля контактов. Современная плата может содержать десятки слоев. Отчасти получить желаемую информацию о качестве установки этих элементов можно при помощи установки рентгеновского контроля, хотя это и усложнит производственный цикл. Но в нашей статье мы ведем речь только о методах электрического контроля.

JTAG

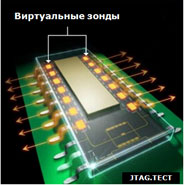

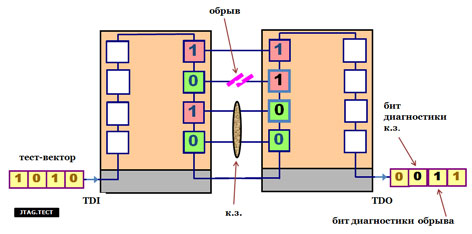

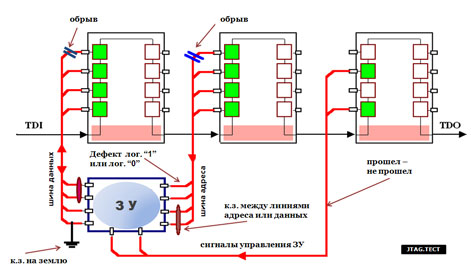

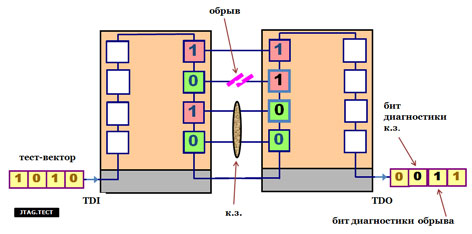

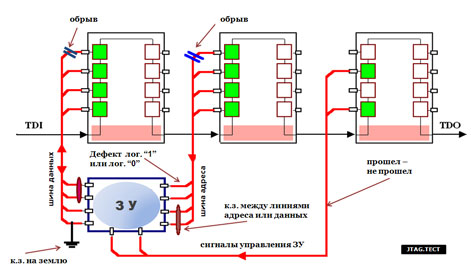

Совершенно иной с точки зрения доступа подход – это внутрисистемное тестирование или, как его еще называют, граничное сканирование (Boundary Scan). Суть метода заключается в тестировании платы через специальный небольшой разъем при помощи 4-проводного интерфейса (опционально может быть и 5-проводным), закрепленного стандартом IEEE 1149.1 еще в 1990 году. Этот интерфейс также часто называют JTAG-интерфейсом по названию группы специалистов, которые занимались его разработкой в период с 1985 по 1990 годы (Joint Test Access Group). Имея в составе устройства одну или несколько микросхем, поддерживающих стандарт IEEE 1149.1, можно протестировать не только цепи, связанные с этими микросхемами, но и остальные элементы, включая память, логику, резисторы и внешние разъемы. При переходе в режим граничного сканирования JTAG-компоненты отключают свою основную логику и переходят в режим тестирования, позволяя внешнему оборудованию управлять своими выводами и тестировать цепи. Инструменты, предназначенные для тестирования по JTAG-интерфейсу, позволяют также произвести внутрисистемное программирование Flash-памяти и ПЛИС. Огромное количество микросхем, используемых в современных разработках, поддерживают стандарт IEEE 1149.1 – это требование современной электронной индустрии. Достаточно упомянуть среди них сигнальные процессоры Texas Instruments, ПЛИС от Altera, Xilinx и Lattice, процессоры Qualcomm и многие другие. Вполне возможно, что ваша разработка уже готова к граничному сканированию, так как производители микросхем уже заложили в них избыточную тестовую логику.

Совершенно иной с точки зрения доступа подход – это внутрисистемное тестирование или, как его еще называют, граничное сканирование (Boundary Scan). Суть метода заключается в тестировании платы через специальный небольшой разъем при помощи 4-проводного интерфейса (опционально может быть и 5-проводным), закрепленного стандартом IEEE 1149.1 еще в 1990 году. Этот интерфейс также часто называют JTAG-интерфейсом по названию группы специалистов, которые занимались его разработкой в период с 1985 по 1990 годы (Joint Test Access Group). Имея в составе устройства одну или несколько микросхем, поддерживающих стандарт IEEE 1149.1, можно протестировать не только цепи, связанные с этими микросхемами, но и остальные элементы, включая память, логику, резисторы и внешние разъемы. При переходе в режим граничного сканирования JTAG-компоненты отключают свою основную логику и переходят в режим тестирования, позволяя внешнему оборудованию управлять своими выводами и тестировать цепи. Инструменты, предназначенные для тестирования по JTAG-интерфейсу, позволяют также произвести внутрисистемное программирование Flash-памяти и ПЛИС. Огромное количество микросхем, используемых в современных разработках, поддерживают стандарт IEEE 1149.1 – это требование современной электронной индустрии. Достаточно упомянуть среди них сигнальные процессоры Texas Instruments, ПЛИС от Altera, Xilinx и Lattice, процессоры Qualcomm и многие другие. Вполне возможно, что ваша разработка уже готова к граничному сканированию, так как производители микросхем уже заложили в них избыточную тестовую логику.

Разработкой тестовых установок для граничного сканирования и внутрисистемного программирования занимается множество компаний, и, в частности, наши партнеры - компания JTAG Technologies. Эта компания занимается структурным тестированием практически со времени появления стандарта IEEE 1149.1. Базируясь в Нидерландах, компания так же имеет свои офисы и представительства в большинстве стран Европы, в США, России, Китае и многих других странах, что говорит о достаточно большой и постоянно растущей популярности граничного сканирования.

Программное обеспечение позволяет не только генерировать тестовые программы, но и производить оценку тестового покрытия вашего устройства, помогая тем самым разработчику добиться более высокой тестопригодности новых разработок. Генерация тестов происходит автоматически на основе схематики, разработанной в любой из существующих САПР, и BSDL-моделей JTAG-компонентов. BSDL – это язык, описывающий тестовую инфраструктуру компонента (Boundary Scan Description Language). BSDL-модели довольно легко загрузить с сайтов производителей микросхем или выбрать из готовой библиотеки. В итоге весь процесс подготовки тестов занимает пару дней. Для программирования flash-памяти также используются готовые модели устройств, входящие в состав программного обеспечения. Программный пакет содержит необходимые инструменты для визуализации обнаруженных при тестировании дефектов.

Следует отметить, что граничное сканирование можно осуществлять и на системном уровне. Несколько устройств, объединенных в одну системную плату, могут иметь общую JTAG-шину граничного сканирования и тестироваться в составе сложного изделия через один единственный разъем. Такое решение часто используется при производстве телекоммуникационного оборудования.

Следует отметить, что граничное сканирование можно осуществлять и на системном уровне. Несколько устройств, объединенных в одну системную плату, могут иметь общую JTAG-шину граничного сканирования и тестироваться в составе сложного изделия через один единственный разъем. Такое решение часто используется при производстве телекоммуникационного оборудования.

Многие предприятия, в особенности оборонного и аэрокосмического приборостроения, практикуют проведение испытаний изделий в стрессовых условиях (критические температуры, повышенная влажность и т. п.). В этом случае граничное сканирование также является незаменимым помощником, так как позволяет проводить тестирование и определять «слабые» места на плате непосредственно в камере для испытаний.

При тестировании сложных цифровых устройств граничное сканирование является наиболее оптимальным методом, учитывая относительно невысокую стоимость оборудования, низкие трудозатраты, а также то, что возможность тестирования уже заложена во многие цифровые микросхемы. Использование граничного сканирования позволит создать единую инструментальную базу на всем предприятии и упростит взаимодействие разрабатывающих подразделений, опытного и серийного производства, обеспечивая легкий переход к политике структурного тестирования. А применение граничного контроллера и программного обеспечения на производстве позволит сформировать универсальное рабочее место для тестирования, программирования ПЛИС и flash в рамках одной операции, используя при этом довольно простое и недорогое оборудование. При этом как разработчики, так и производственный персонал избавляются от рутины диагностики неисправностей в цифровой части изделия.

Вы можете заказать у нас монтаж печатных плат с тестированием качества монтажа с помощью JTAG

«

Технические обзоры